Makefile

Compiling and Linking

Compiling and linking are two critical steps in the process of turning human-readable source code into an executable program. Here's an overview of what each step involves:

1. Compilation

Compilation is the process of transforming source code (written in languages like C, C++, etc.) into machine code or an intermediate format like object code. The compiler reads your source code and checks it for errors, syntax correctness, and other issues. If everything is correct, it translates the code into machine-level instructions that the computer's CPU can understand.

The input issource code(e.g.,.c,.cppfiles).The output isobject files(e.g.,.oor.objfiles), which contain machine code but are not yet complete programs.

Example:

For a C program with the following source code file main.c:

#include <stdio.h>

int main() {

printf("Hello, world!\n");

return 0;

}The compiler (gcc, clang, etc.) will transform main.c into an object file (main.o), which contains compiled code but isn't yet executable.

Key Points:

- Compilers translate high-level code into lower-level object code.

- Object files are incomplete and need linking to be fully functional

2. Linking

Linking is the process that combines object files and libraries into a complete, runnable program. This step is necessary because most programs are made up of multiple parts, often spread across several files. Additionally, programs rely on external code from libraries (like the C standard library for functions like printf).

There are two types of linking:

- Static linking: The linker copies the required code from libraries into the executable itself.

- Dynamic linking: The program is linked to shared libraries (e.g.,

.soor.dllfiles) that are loaded at runtime. This reduces the executable size but requires the shared libraries to be available when the program runs.

The output of the linking step is an executable file (e.g., a.out on Unix-based systems or my_program.exe on Windows).

Example:

Suppose main.o needs to be linked with a standard library like libc to resolve the printf function. The linker combines main.o with the necessary libraries, producing an executable my_program.

Key Points:

- Linkers resolve references to external symbols (e.g., functions or variables) that are not defined within the same object file.

- The linker combines the necessary pieces to create a final executable program.

Summary

Here’s a breakdown of how it works in sequence:

1. Compilation

-

Step 1: Each source file is independently compiled into an object file.

- The source code (e.g.,

.c,.cppfiles) is translated into machine code by theBuildcompiler. - Each

- source file produces a corresponding object file (e.g.,

.oor.obj). - These object files are still incomplete because they often refer to functions or variables defined in other files or libraries.

CompilationOutput:ConvertsOnesourceorfiles intomore object files (machine.o,code).obj).

ProcessExample:

Example:main.c→main.ofoo.c→foo.o

- The source code (e.g.,

2. Linking

-

Step 2:

CombinesAll the object files, along with any necessary libraries, are linked together to form an executable.- The linker combines the object files

andinto a complete program, resolving references between them (like calling functions defined in different files). - It also pulls in any external libraries

to(suchcreateasantheexecutable.standard C library for functions likeprintf). - Output: A final executable (e.g.,

my_program,a.out, ormy_program.exe).

Example:

Example:main.o + foo.o + bar.o + standard→librarylibrariesmy_program

- The linker combines the object files

In

Why Is It a projectTwo-Step withProcess?

This sourceseparation files,into liketwo main.c,steps foo.c,allows andfor bar.c,modular eachcompilation:

- You don't need to recompile all the files every time you make a small change to one file. Only the modified file

wouldneedsfirstto becompiledinto separate object files (main.o,foo.o, andbar.o),recompiled, and then the linkerwould combine them intocombines thefinalnewexecutable.object file with the existing ones to create the updated program. - It supports the reuse of precompiled object files or libraries, making the build process faster and more efficient in larger projects.

Why do Makefiles exist?

Makefiles automate this process by managing the compilation and linking of multiple files in large projects.

A Makefile is a special file used by the make utility to automate the build process of software projects. It defines a set of rules that dictate how to compile and link programs. When working on a project with multiple source files and dependencies, a Makefile can greatly simplify the build process by specifying:

-

Targets: These are typically files that you want to generate, like executables or object files. A target can also represent a task, like running tests or cleaning up compiled files.

-

Dependencies: Files or targets that must be up-to-date before a target can be built. For example, a

.cfile depends on a corresponding.hheader file. -

Commands: Shell commands to be executed to build the target. These typically include commands like

gccfor compiling org++for linking.

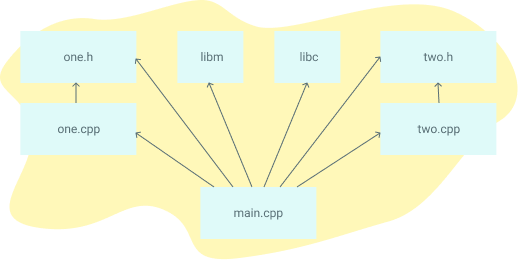

Here's an example dependency graph that you might build with Make. If any file's dependencies changes, then the file will get recompiled:

Interpreted languages like Python, Ruby, and raw Javascript don't require an analogue to Makefiles. The goal of Makefiles is to compile whatever files need to be compiled, based on what files have changed. But when files in interpreted languages change, nothing needs to get recompiled. When the program runs, the most recent version of the file is used. However, it can automate tasks in other environments, like managing dependencies in a Python or JavaScript project.

Make file Basic Structure:

target: dependencies

command

Example Make file for Simple C++ project

# Compiler and flags

CC = gcc

CFLAGS = -Wall -g

# Target program

TARGET = my_program

# Source files

SRCS = main.c foo.c bar.c

# Object files (generated from source files)

OBJS = $(SRCS:.c=.o)

# Default target

all: $(TARGET)

# Rule to build the target program

$(TARGET): $(OBJS)

$(CC) $(CFLAGS) -o $(TARGET) $(OBJS)

# Rule to build object files from source files

%.o: %.c

$(CC) $(CFLAGS) -c $<

# Clean rule to remove generated files

clean:

rm -f $(OBJS) $(TARGET)

Key Points:

$(CC)and$(CFLAGS): Variables for the compiler and flags.$<and$@: Special automatic variables where$<refers to the first dependency, and$@refers to the target.cleantarget: Commonly used to delete object files and executables after building.

Why Use Makefiles?

- Efficiency: Only recompiles files that have changed.

- Automation: Simplifies repetitive tasks like compilation, linking, or testing.

- Portability: Works across different systems without needing to write custom build scripts.